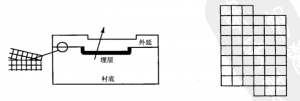

与<111>向相关的晶圆生长问题是图形偏移(pattern)当淀积的速率太高和薄膜在生长时相对于晶圆表面存在角度时,就会发生图形偏移。当依赖于薄膜表面台阶的位置与衬底的图形对准时,图形偏移就成了问题(参见下图)。另一个生长中的主要问题是滑移(slip)。滑移来源于对淀积参数的控制不当,并将导致晶格沿分界面方向滑移(参见下图)。

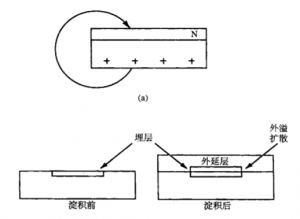

有两个问题与淀积温度相关:自动掺杂(autodoping)和外溢扩散。当晶圆背面的掺杂原子从晶圆中扩散出去时,与反应气体混合后融合到生长的薄膜内,导致生长膜的自动掺杂(参见下图),从而引起薄膜的电阻率和电导率的变化。在N型晶圆上生长的p型薄膜中的自动掺杂将比预想的p型中要低一些。P型浓度较低,是因为自动掺杂的原子中和了一些薄膜内的P型原子。

外溢扩散(out-diffusion)有着同样的影响,但其发生在外延膜和晶圆的交接面。外溢扩散的原子来源于外延淀积前扩散到晶圆内的掺杂源。在双极型器件内,该区域被称为埋层(bunedlayer)或子集电极(subcollector)。通常,埋层是在P型晶圆内的N型区,上面是生长的N型外延层。在淀积过程中,N型原子扩散出来与外延膜的底部结合,使浓度发生变化。极端情况下,埋层可能扩散出来,进入到双极型器件的结构内,引起电性能失效。

CMOS外延:到20世纪70年代后期,外延膜的主要应用是作为双极型晶体管的集电极,该技术为器件工作和灵活地隔离相邻器件提供了高质量的衬底。较新的或着是更主要的应用是用于CMOS电路的晶圆。CMOS电路中存在被称为“闩锁”(latch-up)效应的问题,该问题提出了对外延层的需要。

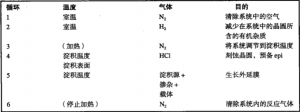

外延工艺:典型的外延工艺开始前,对晶圆表面进行彻底、严格地清洗,然后将晶圆装入淀积反应室内。在淀积反应室内,通过一系列的步骤来保证正确的淀积薄膜。下图给出了一个典型的SiC14的外延工艺。起始的步骤是:对晶圆表面进行气相清洗。清洗之后进行淀积,并伴随着循环的清洗冷却。在所有的步骤中,温度和气体的流量是工艺控制的关键。

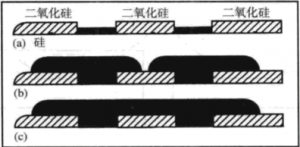

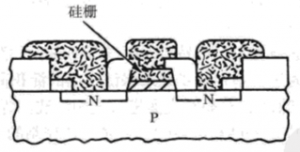

选择性外延硅:外延淀积系统的先进性引发了外延膜的选择性生长。尽管用于双极型晶体管和CMOS衬底的外延膜淀积在整个晶圆上,但在选择性生长当中,它们是通过二氧化硅或氮化硅膜进行生长的。晶圆被放置在反应室内,外延膜直接生长在暴露孔底部的硅上(参见下图)。薄膜生长时,它会与晶圆表面下晶体形成定向。这种结构的优点是在外延区域形成的器件由氧化物或氮化物相互隔离。

如果在隔离的表面继续淀积,薄膜的结构则转化为多晶结构。延伸淀积的另一个结果是覆盖的淀积层变成全部的外延性质。所有这些结果,增加了对高级器件设计在结构上的选择。

多晶硅和非晶硅淀积

直到20世纪70年代中期,随着硅-栅MOS器件的出现(参见下图),多晶硅才在器件结构中得以应用。硅一栅器件技术加速了淀积多晶硅薄膜的可靠工艺的需求。到20世纪80年代,多晶硅似乎成了先进器件材料的主力军。除了MOS栅之外,多晶硅还用于SRAM器件中的负载电阻、沟槽填充;EEPROM中的多层聚合物、接触阻隔层;双极型器件的发射极和硅化物金属配置中的一部分。

早期的工艺仅仅涉及将覆盖有氧化物的晶圆放在水平式APCVD系统中,并在氧化物上淀积多晶硅。多晶硅的淀积和外延淀积的主要区别是硅烷(Silane)的使用。硅烷没有受到外延膜淀积的青睐,而在多晶硅淀积中得到了广泛的应用。

典型的多晶硅淀积工艺的温度是在600℃-650℃的范围。淀积可能来自100%的硅烷或含有或H2的气体。多晶硅的结构在前面描述过,如硅原子在整体上的无序排列。在淀积多晶硅时,结构有些不同。在淀积的起始阶段,温度在575℃下,结构是非晶态的。淀积工艺形成的多晶结构由单晶硅的小核(晶体或晶核)组成。单晶硅被晶核的边界分隔。这种结构称为柱型多晶(columnar poly)。

薄膜的电流特性显示出晶核的尺寸和边界一致性的重要性。当电流流经核边界时,形成电流阻力。核边界越大,电阻越大。要获取器件之间及器件内部持续的电流,需要对多晶硅结构给予良好的控制。为此,在气体流中加入H2,其好处之一是降低了晶圆表面的不纯度和潮湿。随之,导致成核尺寸的减小。在系统中,潮气和不纯净的氧气会引起结构内部二氧化硅的生长,而二氧化硅增加了薄膜的电阻和在后续的掩膜工艺中的刻蚀能力。

所有的系统常规工作参数(温度,硅烷浓度,抽真空速率,氮气流量,或其他气体流量”)都会影响淀积率和成核尺寸。通常,晶圆在600℃左右淀积后进行退火,进一步形成对薄膜的晶体化。无论什么时候,当晶圆通过高温工艺,都会产生再晶体化过程。因此,在完整的器件或电路上的多晶硅薄膜的成核尺寸和电参数与淀积时的薄膜是完全不相同的。