概述

我们在前面的章节中已经对芯片制造的一些基本工艺流程进行了介绍,相信大家已经对这些基本工艺有了一定的了解。在芯片加工完之后,如何保证芯片在外界复杂的环境下保持优良的性能,这是本节要讲的主要内容。

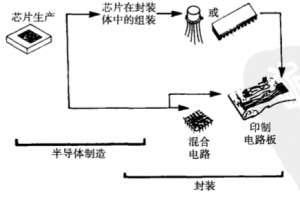

当晶圆表面上的芯片完成了晶圆电测以及确定了电路功能运行正常的芯片后,芯片将会被封装到一个单独的保护性封装体中,与其他的器件以混合形式或多芯片模块(MCM)安装在一起,或直接与印制电路板连接。本章将描述用于保护芯片和将芯片进行电连接的封装及其工艺,依次允许将电路集成到更大的电子系统中。

本节我们将了解:

l.半导体封装器件的4项功能。

2.封装体中的5个常见组件。

3.主要的封装设计。

4.主要的封装工艺流程。

简介

晶圆电测后,每个芯片仍是晶圆整体中的一部分。在应用于电路或电子产晶之前,单个芯片必须从晶圆整体中分离出来,多数情况下,被置人一个保护性的封装体中。这些芯片也可以直接安装在陶瓷衬底的表面作为混合电路的一部分,或与其他芯片一起安装到一个大型的封装体中,作为多芯片模块(MCM)的一部分,或直接安装在印制电路板上,或做成“板上芯片”(COB)或直接贴芯片(DCA参见下图)。这三种封装形式分享一些共同的工艺。除了保护芯片、封装工艺提供和系统的电连接,可以使芯片集成到一个电子系统中,并且提供环境保护和散热。这一系列工艺称为封装(packaging)、组装(assembly)或后端工序。在封装工艺中,芯片称为”dies”或”dice”。

多年以来,半导体封装业由于受工艺复杂程度及制造业需求的影响而滞后于芯片制造业。伴随VISI/UISI时代的到来,芯片密度的提高迫使封装技术及自动化生产不得不进行极大的升级和改进。

更高密度的芯片要求更多的输人(I)和输出(O)连线点。这些称为I/O数,或简单地称为引脚数。SIA技术路线图(ITRS)预测到2007年引脚数将增至3左右(参见下图)。IRTS将引脚数、成本、尺寸、厚度和温度列为封装技术的主要的物理推动者。随着固体电路应用领域的不断拓展,对特殊封装设计的需求大大提高了。更多引脚数已经导致凸点/倒扣芯片技术的采用。尺寸和速度的考虑已经促使在客户定制产晶中芯片级封装的使用,例如,手机和手持产晶。太空的恶劣环境、汽车及军用产晶对封装有苛刻的要求,这些要求特殊的封装、工艺以及测试来保证在此环境下器件的高度可靠性。这些封装、工艺和测试称为”hi-rel”(高可靠性类)。其他领域的芯片及封装称为商用(commercial)类。

封装业早已不再是半导体工业界的继子了。很多人认为封装业最终会成为芯片尺寸大小增长的限制因素。然而,从当前发展来看,人们更关注于新的封装设计,新的材料开发及更快、更可靠的封装工艺。