由于MOS元件的优点是密度比较大,所以相邻元件之间的隔离区域就比较小。不同的隔离设计将会在下面讨论。MOS元件的另一个优点是在工作中功耗低。首先,MOS晶体管在电路中是“关”的状态,不消耗能量,不像双极型晶体管那样在电路中一直要保持“开”的状态,从而会产生热。其次,MOS晶体管作为电压控制器件,在工作中,需要的能量比较低。CMOS的设计需要的能量会更低。

MOS电路最初的优点是工艺步骤比较少,而且芯片尺寸比较小,从而使芯片的成本较低且良品率较高。随着MOS电路发展到VISI/ULSI,由于需要添加很多工艺步骤,MOS电路的最初优点已经不存在了。一般来说,人们更倾向于使用开关速度较快的双极型电路做逻辑电路。而在存储器电路中,人们一般采用MOS电路,因为它的尺寸小且耗能低。到20世纪80年代,由于双极型电路和MOS逻辑电路的广泛应用,这些传统的用法已经变得模糊。关于这个主题,我们将在后面做更详细的讨论。

双极型电路的形成

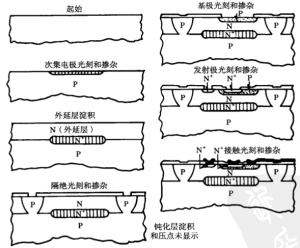

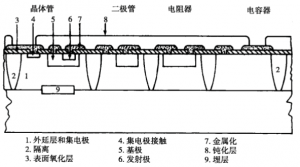

结隔离:关于双极型电路的结构和基本性能我们已经讨论过了。然而,要把晶体管和其他的器件合并起来形成电路还需要另外一些结构。这些基本的结构包括隔离设计和低电阻率的集电极接触。如果两个晶体管或者其他的两个器件互相毗邻,它们会因为短路而不工作(参见下图),对早期的集成电路设计者的一个挑战就是找到一种把不同的元器件隔离开来的方法。这种需求促使了外延层(EPI)双极型结构的诞生(参见下图)。

这种过程是从p型晶圆开始的,在p型晶圆上进行N型扩散(这个过程图标没有显示进行扩散所需要的氧化和光刻步骤)。在N型扩散之后,在芯片的表面淀积上一层N型的外延层,这样一来,就把N型扩散的区域“埋伏”在外延层下面。众所周知,N型区域称为埋层(buried layer)或晶体管的次集电极。它的作用是,当电流从基极出来流向芯片表面集电极时,给集电极电流提供一个低电阻的通道。

外延层淀积之后,将其氧化并且在埋层的两边各开一个孔。同时要进行p型掺杂步骤,并使达到P型芯片的表面。这个掺杂步骤将外延层孤立成一个”N型小岛”,因为它的每边(P型掺杂区)和底部(P型芯片)都被P型掺杂所包围。每个“孤岛”上所形成的元器件就被相互隔离开了(参见下图)。因为连在电路中的PN结处于反偏模式状态,所以每个元器件是相互绝缘的。也就是说,没有电路流过PN结。这种设计称为“结隔离”(junction isolation)或者“掺杂结隔离”(doped junction isolation)。

介电质隔离:在高辐射的环境中,比如在太空或者离原子能武器较近的地方,掺杂的结会产生电子或者空穴,从而会破坏结的功能。这不仅会使元器件失效,而且这种辐射还会淹没对掺杂区的保护。介质隔离设计将会给我们提供所需要的电绝缘和辐射保护。