物理性保护

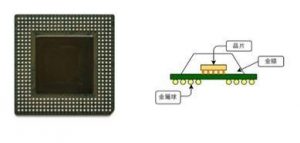

封装体的第二个功能是物理性保护,防止芯片破碎、免受微粒的污染和外界损伤。所需求的物理性保护程度有高有低,低到消费类产品的应用,高到要求十分苛刻的汽车电子、太空火箭和军事领域的产品应用。实现此保护功能的方法是将芯片粘贴一个特定的芯片安装区域,然后用适当的封装体将芯片、连线、封装体内部引脚封闭起来。芯片的尺寸和最终应用领域决定了封闭材料的选择以及封装体的设计及其尺寸。

环境性保护

封装外壳的另一功能是对芯片的环境性保护,可使其免受化学品、潮气和其他有可能干扰芯片正常功能的气体对其产生的影响。

散热

所有的半导体芯片在工作时都会产生一定的热量。有些芯片会产生大量的热。对大多数芯片来说,封装体封闭的各种材料本身可带走一部分热量。当然,选择封装材料的一个因素是看其散热特性。对产生大量热的芯片,需额外考虑其封装设计。这种另行的考虑会影响封装体的尺寸,同时大多数情况下要求额外地安装于封装体上的金属散热条或块。

封装操作工艺的概述

本节提供对主要封装工艺流程的概述。

洁净度和静电控制

芯片在其整个使用寿命的期限内对污染物攻击的易损性将长期存在。虽然封装区域对洁净度水平的要求远不如芯片生产区域要求高,保持一定的洁净度仍是非常重要的。图1&6的表中列举了常见的污染物和静电控制的实施方案。高可靠性芯片的生产区域通常来讲需要更高的洁净度。实际上,许多公司都意识到了如果污染物控制的方案不得要领,其产品是注定要失败的。因此,更多的封装区域实行了非常严格的控制,尤其是对化学品和人体产生的颗粒物的控制。

在封装区域内来自于外界环境的最致命危害是静电。在芯片生产的洁净室内,对静电的控制主要是防止颗粒物吸附到芯片的表面。这同时也是封装区域所关心的一个话题。但最关注的是静电放电(electrostaticdischarge)问题,或称为ESDO静电累积可以产生高达数万伏的电压。如果如此高的电压突然在芯片表面放电,将很轻易地损坏电路部分。金属氧化物半导体(MOS)栅电路结构尤其易受静电放电的损害。

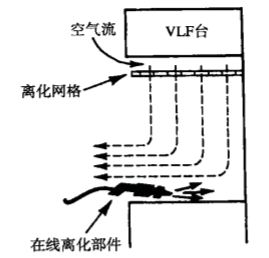

每个生产高集成度芯片的封装区域应有一套切实有效的防静电方案(参见下图)。对生产军用器件的封装厂来说,所提供的防静电方案将是能否得到订单的必要条件之一。防静电方案的实行是靠生产操作员配带接地的腕带和无静电工作服;使用防静电材料的搬运载体;搬运产品时用升降式设备而不用推拉式设备;生产设备,工作台面及地板垫均要接地。减少静电的其他方法还有在氮气和空气混合气的气枪上(参见下图),以及从HEPA滤芯中流出的空气通道上安装电离器。