11.6推进氧化

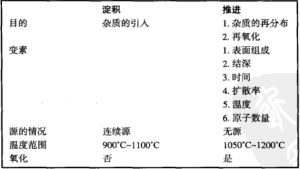

扩散工艺的第二个主要部分就是推进氧化步骤。它的不同称谓有推进(drive-in),扩散(diffusion),再氧化(reoxidation)或reoxo这一步的目的是双重的:在晶圆的杂质再分布和在暴露的硅表面再生长新的氧化层

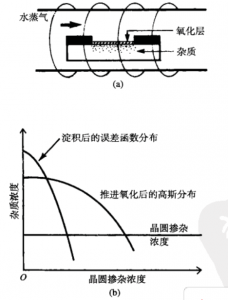

1.杂质在晶圆中向更深处的再分布。在淀积过程中,高浓度但很浅的杂质薄层扩散进晶圆表面。推进过程没有杂质源。就像喷雾瓶按下喷嘴后喷出的物质会不断地扩散到整个房间一样,仅是热推动杂质原子向晶圆的更深度和更广度扩散。在此步中,淀积所引入的原子数量(Q)恒定不变。表面的浓度降低,原子形成新的形状分布。推进步骤后的分布在数学上用高斯分布来描述(参见下图)结深的增加。通常,推进氧化工艺的温度高于淀积步骤。

2.推进氧化的第二个目的就是暴露的硅表面的氧化。炉管中的氛围是氧气或水蒸气,杂质向晶圆推进的同时进行氧化。

推进氧化的设置、工艺步骤和设备与氧化相同。推进完成后,晶圆会再次被评估。测试陪片(来自淀积步骤)会再次被四探针测试表面浓度,器件晶圆会被检测洁净度。测试陪片用于测量结深并有可能用于测量可动离子的污染。一些扩散步骤后,会对工程电路芯片上的测试结构进行电测试以获得结的参数。

11.6,1氧化的影响

晶圆表面的氧化影响到杂质的最终分布。这种影响与表层杂质氧化后的易位有关。回想一下,硅的氧化是需从表面开始消耗硅的。要问的问题是,表层的杂质发生了什么?答案由杂质的导电类型而定。

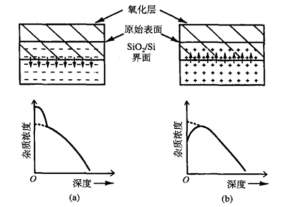

如果杂质为N型,发生所谓的堆积效应(pile-up)[参见下图]。当氧化物一一一硅的界面提升到表面时,N型杂质原子会向硅中分凝,而不是氧化物中。这个效应增加了硅的新表层中杂质的数量。换言之,N型杂质在晶圆表面堆积,杂质的表面浓度增加。堆积效应改变器件的性能。

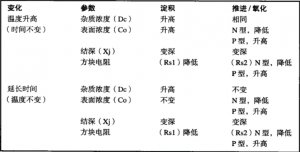

如果杂质为P型的硼,会发生相反的效应。硼原子更容易溶在氧化层中,并被吸到氧化层中[参见下图]。对晶圆表面的影响是降低了硼原子的浓度,从而也影响到器件的电性能。下图列出了对淀积与推进氧化的总结。下图显示了淀积与推进步骤对扩散电参数的影响。

11,7离子注入简介

高集成度电路的发展需要更小的特征图形尺寸与更近的电路器件间距。热扩散对先进电路的生产有所限制。5个挑战是横向扩散、超浅结、粗劣的掺杂控制、表面污染的干涉和错位的产生。横向扩散不仅发生在淀积和推进中,并且每次晶圆受热到扩散运动可以发生温度的范围都会继续,如下图所示。电路设计者必须给相邻区间留出足够的空间以避免横向扩散后各区间的接触短路。对于高密度电路的积累效果可能是很大程度上增加了管芯的面积。高温的另外一个问题就是晶体损伤。每次晶圆被升温、降温都会发生位错导致的晶体损伤。高浓度的此种位错可能导致漏电流引发的器件失效。先进工艺程序的目的之一就是减小热预算(thermal budget)以减弱这两个问题。

MOS晶体管的发展产生了两个新的要求:低掺杂浓度控制和超浅结。高效MOS晶体管要求栅区的掺杂浓度小于10的15次原子/Cm2。然而,扩散工艺很难实现这一级别上的一致性。为了实现高封装密度而按比例缩小的晶体管也需要源漏区的浅的结深圃。对0.18um设计规则水平,结深在40nm范围,对亚0.1um范围设计,结深会在20nm的范围。

第4个问题由掺杂区的物理/数学引出。下图所示,杂质原子的大部分靠近晶圆表面。这使得电流的大部分会在杂质主要分布的靠近表面区流动。遗憾的是,这个区域(晶圆内和表面)与沾污干扰或电流退化区相同。先进器件所需的,在晶圆表面具有特定杂质梯度的特殊阱区无法由扩散技术来实现(参见下图)。这些阱区使高性能晶体管得以实现。

离子注入克服了扩散的限制,同时也提供了额外的优势。离子注入过程中没有侧向扩散,工艺在接近室温下进行,杂质原子被置于晶圆表面的下面,同时使得宽范围浓度的掺杂成为可能。有了离子注入,可以对品圆内掺杂的位置和数量进行更好的控制。另外,光刻胶和薄金属层与通常的二氧化硅层一样可以作为掺杂的掩膜。基于这些优点,先进电路的主要掺杂步骤都采用由离子注入完成就不足为怪了。扩散还可以被用在非关键层的掺杂及低集成度的电路上。

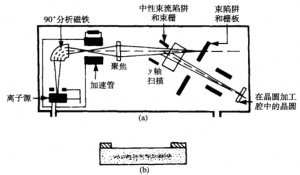

11.8离子注入的概念

扩散是一个化学过程。离子注入是一个物理过程,也就是说,注入动作不依赖于杂质与晶圆材料的化学反应。火炮将炮弹打入墙中就是一个展示离子注入概念的示例(参见下图)。从火炮的火药中获取足够的动量,炮弹会射入墙体,在墙体表面以内停止。离子注入过程中发生相同的情形。替代炮弹的是离子,掺杂原子被离化、分离、加速(获取动能),形成离子束流,扫过晶圆。杂质原子对晶圆进行物理轰击,进入表面并在表面以下停止[参见下图]。