11,3,4同型掺杂

一些器件需要同型的掺杂,所掺杂质与原有杂质类型相同。换言之,在N型晶圆中掺入N型杂质或在P型晶圆中掺入p型杂质(参见图11.8)。此种情况下,加入的杂质原子仅仅在限定区域中提高了杂质原子的浓度,不会形成结。

在半导体器件的截面图中(参见下图),NP结被简单地显示为器件内部的区域。没有图形代表N型或P型区域。截面图仅仅显示掺杂区域和结的相对位置。这种类型的图基本不提供杂质原子浓度的信息而仅仅估计区域的实际尺寸。在图中,20mm的厚晶圆上只有2um深的结,当晶圆厚度按比例变为8英尺时,结深仅仅变为0.4英寸。

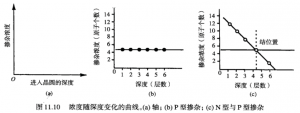

11.3.6浓度随深度变化的曲线

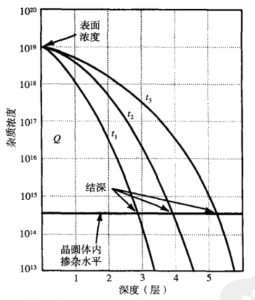

另外一种显示掺杂区域的两维图形是浓度随深度变化的曲线。这种图形的纵坐标为杂质的浓度而横坐标为距晶圆表面的深度。下图给出了这种图形的一个例子。这个图例中所用的数据来自下图所示的掺杂示例。首先,画出了P型掺杂的浓度。示例中,纵深方向的5个层中刚好有5个P型杂质原子[(参见下图)]。其次,N型杂质的原子数量也被标示出来。由于原子的数量随着深度的增加而减少,所画线段向右下方倾斜。在第4层,N型与P型杂质数量相当,两线交合。这是图形方式显示结的位置。

对于实际的工艺而言,外来掺杂的浓度随深度的纵剖面图不是一条直线。它们是曲线,曲线的形状是由掺杂技术的物理特性决定的。曲线的实际形状在淀积和推进中介绍。

11.4扩散工艺的步骤

在半导体晶圆中应用固态热扩散工艺(solid-state thermal diffusion)形成结需要两步。第一步称为淀积(deposition),第二步称为推进氧化(drive-in-oxidation)。两步都是在卧式或立式炉管中进行的。

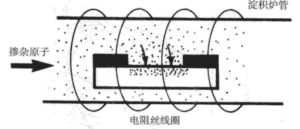

11.5淀积

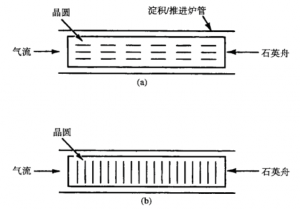

扩散工艺的第一步称为淀积,也称为预淀积(predeposition,dep,predep)。这一步在炉管中进行,晶圆位于炉管的恒温区中。掺杂源位于杂质源箱中,它们的蒸气以所需的浓度被送到炉管中(参见下图)。

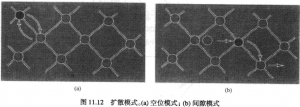

在炉管中,杂质原子扩散到裸露的晶圆中。在品圆内部,掺杂原子以两种不同的机制运动:空位模式和间隙运动。空位模式中[参见下图]掺杂原子通过占据晶格空位来运动。第二种模式[参见下图]依赖于杂质的间隙运动。在这种模式中,掺杂原子在晶格间运动,即间隙位置。

淀积工艺受几个因素控制或约束。其一,是特定杂质的扩散率(diffusivity)。扩散率计量的是杂质在特定晶圆材料中的运动速率。扩散率越高,杂质在晶圆中的穿越越快。扩散率随温度的上升而变大。

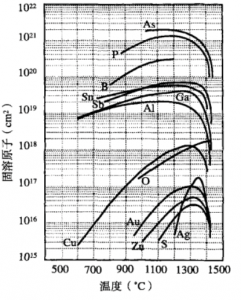

另外一个因素是杂质在晶圆材料中的最大固溶度(maximum Solid solubility)。最大固溶度是特定杂质在晶圆中所能达到的最高浓度。相似的例子是咖啡中糖的最大溶解度。咖啡只能溶解一定量的糖,而后便会在杯底凝结为固态糖。最大固溶度随温度的升高而升高。

在半导体淀积步骤中,将杂质浓度故意设置为比晶圆材料中的最大固溶度更高。这种情形下,确保晶圆可接受最大掺杂量。

进入晶圆表面的杂质数量仅仅与温度有关,淀积在所谓的固溶度允许条件下进行。硅中不同杂质的固溶度如下图所示。

晶圆中不同层面杂质原子浓度是影响二极管和晶体管性能的重要因素。下图显示了淀积后杂质浓度随深度变化的关系曲线。曲线的形状是特定的,这就是数学中所称的误差函数(error function)。影响器件性能的一个重要参数就是晶圆表面的杂质浓度。这称为表面浓度(surface concentration),是误差函数曲线与纵轴相交处的值。另外一个淀积参数就是扩散到晶圆内部的全部杂质原子数量。这个数量随淀积的时间而增加。计算上,原子的数量(0)由误差函数曲线下方的面积所代表。

11.5.1淀积步骤

淀积分为4步,它们是:

1.预清洗与刻蚀。

2.炉管淀积。

3.去釉。

4.评估

预清洗与刻蚀:淀积前的晶圆要先经过预清洗工艺去除微粒与沾污。所用化学品及工艺与氧化前的清洗相同。预清洗后,晶圆由HF或与水的溶液进行化学刻蚀,以去除晶圆暴露表面上可能长出的氧化物。晶圆暴露在空气中或化学预清洗都可能形成晶圆表面的氧化物。氧化物的去除对于杂质能否阻止进入晶圆表面是必需的。刻蚀时间与浓度必须很好地平衡,以避免掩膜氧化层被去除或变得过薄。

炉管淀积:淀积工艺像氧化工艺一样,最少需要三个循环。第一个循环是上料循环,此过程在氮气环境中进行。第二个循环是淀积掺杂循环。第三个循环是下料循环,此过程也是在氮气环境中进行的。

晶圆在舟上垂直放置(参见图1L15)或与炉管的轴向平行。垂直放置可以达到最大的放置密度,但由于晶圆阻碍气体流动,可能导致均匀度问题。对于均一掺杂,气体在各晶圆间必须混合均匀。平行的放置方式由于气体能无阻碍地在晶圆间流动,从而提供均匀性上的优势,缺点是装片密、度低。在两种放置方式中,都用假片放置在舟的前后端,以保证中间器件晶圆的均匀掺杂。