概述集成电路的制造可以分成两个主要的部分。首先,在晶圆内及其表面制造出有源器件和无源器件,这称做前端工艺线或者FE。L。在后端工艺线(BEOL)中,需要在芯片上用金属系统来连接各个器件和不同的层。在这一章中,金属化工艺所要用到的材料、规范、工艺将随着金属在芯片制造中的应用而逐步阐明。用在CVD、蒸发、离子注人和溅射系统的真空泵将在这一章的结束时进行介绍。

13,1简介

金属薄膜在半导体技术中最普通的用途就是表面连线。把各个元件连接到一起的材料、工艺、连线过程一般称为金属化工艺(metallization process)。根据器件的复杂度和性能要求,电路可能要求单层金属或多层金属系统。可能使用铝合金或金作为导电的金属。

13.2导体一单层金属

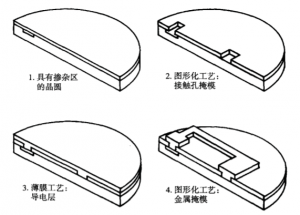

在中规模集成电路时代,金属化工艺相对要简单一些(参见下图),仅需要单层金属的工艺流程。首先在表层刻蚀连接各个器件/集成电路元件的小孔,它们被称为“接触孔”;接在连接孔光刻工艺后,通过真空蒸发、溅射或CVD技术在整个晶圆表面淀积一层导电金属薄层。用传统的光刻和刻蚀工艺或剥离技术将这些层不要的部分去掉;做完这一步之后,芯片表面就留下了金属细线,它们被称为“导线”(lead)、“金属线”(metal line〕或“互相连接”(inter connect)。通常来说,为了确保金属和芯片之间具有较好的导电性能,经褙在金属的光刻之后加人一个热处理步骤,或者称做“合金化”(alloying)过程。

不管金属化系统的结构如何,它必定符合以下的条件:

- 良好的电流负载能力(电流密度)

- 和晶圆表面(通常是S℃2)具有的良好的黏合性

- 易于图形化工艺

- 和晶圆材料具有良好的电接触性能

- 高纯度·耐腐蚀.具有长期的稳定性

- 能够淀积出均匀而且没有“空洞”和“小丘”的薄膜

- 均匀的颗粒结构

13.3导体一多层金属设计

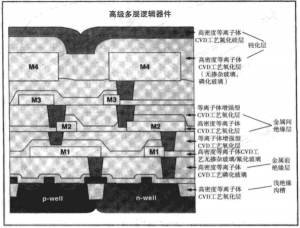

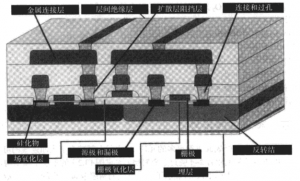

增加芯片密度能够在晶圆表面放置更多的元件,这实际上就减少了表面连线的可用空间。这个两难的问题的解决方法就是利用有2-4层独立金属层(参见下图)的多层金属结构。到2012年,芯片上的金属层可望达到9层,下图显示了一个典型的两层金属的堆叠结构。这种堆叠结构的底部是在硅表面形成的硅化物阻挡层,这有利于降低硅表面和上层之间的阻抗。如果铝作为导电材料的话,阻挡层也能够阻止铝和硅形成合金。接下来是一层介质材料层,可称之为“金属间介质层”(IDL或IMD),它在两个金属层之间提供电绝缘作用。这种介质材料可能是淀积的氧化物、氮化硅或聚酰亚胺膜。这一层需要进行光刻以形成新的连接孔,这些连接孔被称为通孔或塞,它们下到第一层金属。在这些连接孔中淀积导电的材料,就可以形成导电的塞。紧接着,第一层的金属层被淀积并进行图形化工艺。在以后的工艺中,重复IMD一塞一金属淀积一图形化工艺,就形成了多层金属系统。多层金属系统更昂贵,良品率较低,同时需要尽量使晶圆表面和中间层平坦化,才能制造出比较好的载流导线。

导体

铝

这一节将介绍三种主要用于金属连接层的材料。在VLSI集成电路开发之前,主要的金属化工艺材料就是纯铝。通来讲,了解为什么选择铝以及铝的局限性,对于理解金属化工艺系统是很有教育意义的。从导电性能的观点来看,铝的导电性要比铜和金差一些。如果用铜直接替代铝,铜与硅的接触电阻很高,并且如果铜进人器件区将引起器件性能的灾难。而铝则不具有上面所说的问题,

因而成为一种较好的选择。它有足够低的电阻率,有很好的过电流密度。它对二氧化硅有优异的黏附性,有很高的纯度,天然的同硅有很低的接触电阻,并且用传统的光刻工艺易于进行图形化工艺。铝原料可被提纯到5一6个“9”的纯度。