淀积膜

采用CVD技术淀积的薄膜,按电性能可分为半导体膜、绝缘体膜和导体膜。在下面的内容当中,介绍了每一种膜在半导体器件中的主要应用,以及特殊薄膜的使用。这里对特殊薄膜只做概括性的介绍,后面将给出较为细致的解释。导体金属膜的淀积方法也将在后面讨论。

淀积的半导体膜

至此,我们已经讨论了作为半导体器件和电路基础部分晶圆的形成。但制造高质量的器件和电路·体硅(bulk)品圆的使用还存在着一些不足。晶圆的质量、掺杂范围和掺杂的控制等因素限制了体硅晶圆的使用,同时也限制了高性能双极型晶体管的制造。解决的方法是硅淀积,称为外延层(epitaxial layer)。这是业界的主要进展之一。早在1950年,外延层已成为半导体工艺中的一部分“。从那时起,硅淀积工艺便应用到先进的双极型器件的设计及CMOS电路中对质量要求较高的衬底,以及在蓝宝石和其他衬底上的砬外延层的淀积(参见第14章),砷化镓和其他Ill-IV族和Il-VI族薄膜也采用了外延膜的淀积工艺。外延膜具有与衬底材料同样的材料(硅上硅),称为同质外延(hemoepitaxial)u淀积材料不同于衬底材料时(硅上砷化镓),产生的薄膜称为异质外延(heteroe-pitaxial)。

外延硅

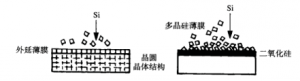

外延〔epitaxial〕一词来源于希腊文,意为“安排在上面,在半导体技术中,指薄膜的单晶结构。在CVD反应室内,硅原子被淀积在裸露的晶圆上,形成单晶结构(参见下图)。当对化学反应剂进行有效控制并且正确设置系统的参数时,具有足够能量的淀积原子到达晶圆表面,并在其表面游动,将自身调整到与晶原子的晶体定向相一致。这样,淀积在<111>晶向的晶上便生长成<ll1>晶向的外延层。

另外,如果晶圆的表面有一层薄的二氧化硅、非晶态层表面或污染物,则会影响淀积原子的正确定位,结果导致薄膜结构为多晶硅。这种情形可在某些方面,如MOS栅中得以应用。但对于单晶的薄膜结构,则并不希望多晶的出现。

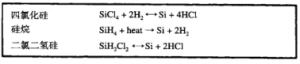

四氯化硅化学源:外延层的淀积可选用一些不同的化学源(参见下图)。在选择硅的化学源上,淀积温度。薄膜质量、生长速率及与特殊系统的兼容性均是考虑的因素。其中,个重要的工艺参数是淀积温度。温度越高,生长速率越快。但过快的生长速率会形成较多的晶体缺陷,产生薄膜裂隙和应力。较高的温度也会造成较高的自动掺杂和扩散外溢(这些效应在下面的章节中描述)。

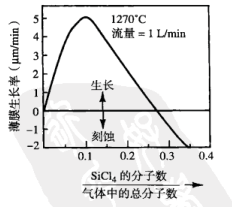

四氯化硅是硅淀积中首选的化学源。它能够允许高的成形温度(生长速率)并具有可逆的化学反应。在下图中,双箭头表示在一个方向进行反应的形成的硅原子,而在另一方向上的反应将硅去除(刻蚀)。在反应室内,这两种反应彼此竟相进行。

最,硅表面被刻蚀,为淀积反应做准备。第二阶段,硅的淀积比刻蚀速率快,产生淀积的薄膜。

下图显示了这两种反应的效果。随着在气体流中增加四氯化硅分子的百分比含量,淀积率首先增加。在比率为0.1时,刻蚀反应开始并起主导作用,减慢了生长速率。起始时,在反应室内主要是薄膜的生长。氯化氢(HCI)气体通过流量计进入反应室,刻蚀掉很薄的一层硅表面,为其后的硅淀积做准备。

硅化学源:硅烷是第二种常用的硅源。硅烷具有不需要第二种反应气体的优点。它是通过受热分解产生硅原子。反应温度比SiCL的反应温度低几百度,从自动掺杂和晶圆弯曲等方面极具吸引力。硅烷也不会产生图形偏移(参见“外延膜的质量”遗憾的是,硅烷在反应时,反应气体遍及整个反应室内,形成粉末状的薄膜而污染晶圆。作为反应源,硅烷在多晶硅和二氧化硅的淀积中有着更多的应用。

二氯二氢硅化学源:二氯二氢硅也是一种用于薄外延膜的低温硅源。较低的温度可减少自动掺杂和在前步工艺扩散埋层中的固态扩散以及提供更加一致的晶体结构。

外延薄膜掺杂:外延薄膜的优点之一就是以工艺达到精细的掺杂和对掺杂范围的挖制。晶圆制造时,其浓度可达到约10的13次到10的19次原子每立方厘米,其上限接近磷在硅中的固态溶解度。

薄膜的掺杂是通过将掺杂气流添加到淀积反应物中的方式获取的。掺杂气体源完全与淀积掺杂反应炉内使用的化学物和输送系统相同。实际效果是CVD淀积反应搴转换成掺杂反应炉。在反应室内,掺杂剂与生长膜相融合,并确定所需的电阻。N型和P型膜能够在N型或P型晶圆上生长。在双极技术中的传统上艺生长的外延膜是在p型晶圆上进行N型外延膜生长的。

外延膜的质量:工艺中首要关注的就是外延膜的质量。除了通常考虑的污染之外,还有一些是外延生长的瑕疵。被污染的系统可能引起被称为薄雾(haze)的问题“。薄雾是一种表面的疑难问题,可从微米级破损变化到可见的从暗不光滑磨面。/薄雾来源于残存在反应气体中的氧气或系统泄露。

在开始淀积时,对淀积表面的污染将引起加速生长·称为“尖刺”(spike)(参见下图)。尖刺的高度可能与薄膜的厚度相同。它们会在光刻餃层或其他的淀积膜中产生洞和断裂。

生长期间可能发生一些结晶问题,其中之一是堆垛层错(stacking faults)。堆垛层错是由于原子面周围产生“位错”的相关原子组成的多余原子面。堆垛层错在表面形成并“生长”到薄膜的表面。堆垛层错的形状依赖于薄膜和晶圆的定向。在<111>11向,薄膜的堆垛层错具有锥形的形状(参见下图);而<l11>面的晶形成方形的堆垛层错。堆垛层错可以采用X射线或刻蚀技术进行检测。